1. 서 론

최근 투명한 특성을 지닌 n-type 결정성 (crystalline) ZnO, InZnO, n-type 비정질 (amorphous) InGaZnO (IGZO)와 같은 산화물 반도체가 차세대 디스플레이의 백플레인 (backplane) 재료로 많은 연구가 이루어지고 있다. 또한 공정이 비교적 단순하고 균일성이 우수하다는 장점으로 인해 비정질 실리콘 (Si)을 대체할 수 있는 재료로 주목을 받고 있다 [1-5].

특히 IGZO 채널 층 기반의 박막 트랜지스터 (thin-film transistor, TFT)는 이동도가 우수하여 전반적인 디스플레이 구동 회로의 적용이 유리하고, 에너지 밴드갭 (energy band gap)이 3 eV 이상이므로 가시광선 영역에서 투명성을 지니기 때문에 투명 소자로 제작이 수월한 장점을 가지고 있다. 하지만 IGZO 채널 층의 구성 물질인 인듐 (In), 갈륨 (Ga)과 같은 희귀 금속의 매우 높은 원가 비용은 최종 생산 단가에 영향을 주므로 여전히 중요한 결점이다 [6-8]. TFT의 생산 단가는 반도체 공정상의 가장 중요시되는 부분 중 하나이므로, 공정 단계에서 칩 크기 (die size)와 실장 비용 (package cost)을 줄이거나 수율 (yield)을 향상시키는 등의 연구가 집중되고 있다. 따라서 여러 연구에서 공정 기술상의 다양한 발전이 시도되고 있지만 IGZO 채널 층에 대한 고질적인 원가상의 문제를 해결하기에는 많은 시간이 소모될 것으로 판단된다.

산소 결핍 구조의 이산화 티타늄 (TiO2-x)은 저렴한 티타늄 (Ti)의 원가와 풍부한 자원으로 인해 고비용 IGZO 채널 층의 대안으로 제안되어 왔다 [9,10]. TiO2-x는 루틸(rutile)의 경우 자외선 영역에 속하는 넓은 energy band gap을 가지고 있으며, 부식과 외부 광원과 같은 환경에 견딜 수 있는 우수한 지속성 및 안정적인 상태를 가지고 있다 [11]. 또한 높은 굴절률과 적절한 유전율로 인해, 다른 산화물 반도체에 비해서 상대적으로 높은 효율을 가지기 때문에 TFT의 채널 층 물질로 많은 주목을 받고 있다.

TiO2-x TFT는 스프레이 열 분해법 (spray pyrolysis) [12-15], 용액 공정 (solution process) [16,17], 펄스레이저 증착법 (pulsed laser deposition) [18-20], 금속-유기물 화학 기상법 (metal-organic chemical vapor deposition) [21], 스퍼터링 증착법 (sputtering deposition) [22-24]과 같은 여러 방법으로 제작되고 있다. 이 중 sputtering deposition 공정은 높은 증착률과 낮은 기판 온도 유지, 비교적 쉬운 박막 조성 제어 등의 장점으로 인해 대량 생산에 상업적으로 높은 잠재력을 가지고 있다 [25-27].

한편 TFT의 채널 층으로서 TiO2-x 박막의 가능성은 다양하게 연구되어 왔지만, RF magnetron sputtering system으로 증착된 후 급속 열처리 (rapid thermal annealing, RTA)에 의해 유도된 루틸 (rutile), 아나타제 (anatase) TiO2-x 채널 층의 전기적, 표면적인 반도체 성능 변화에 대한 조사는 아직 명확하게 분석되지 않고 있다.

따라서 본 연구에서는 대면적 디스플레이의 back plane 제작에 가장 적합하며 다양한 장점을 가지는 공정 방법인 RF magnetron sputtering system으로 TiO2-x 박막을 증착하고 각각 400, 500, 600, 700 °C로 RTA의 온도차를 제작 조건으로 설정하여 post-annealing을 진행하였다. 최종적으로 TiO2-x 채널 층 기반의 TFT를 제작한 후, TiO2-x 박막 표면상의 미세 구조 분석 및 결정체 물질 분자상의 x-ray 조사에 통해서 RTA의 온도 변수가 TiO2-x 결정체 구조적 특성 및 TiO2-x 채널 층 기반의 TFT에 대한 전기적 특성, 전류 지속성과 안정성에 미치는 영향을 조사하였다.

2. 실험 방법

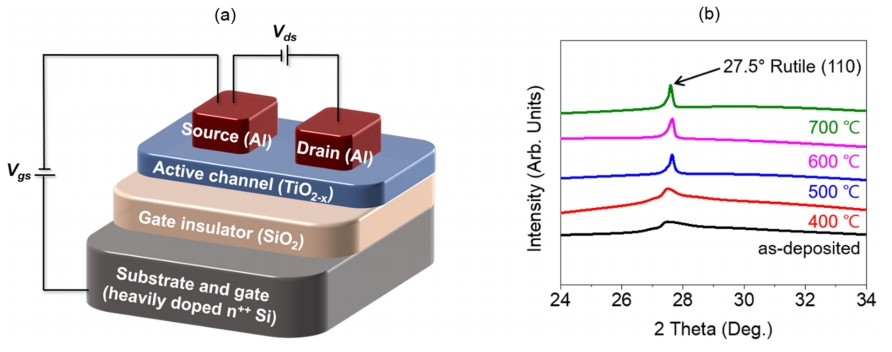

그림 1(a)은 본 연구에서 TC-BG (top contact-bottom gate) 구조로 제작한 TiO2-x 채널 층 기반 TFT의 간략한 도식도를 나타낸다. 하단 부분에 두께 600 μm의 heavily doped n-type Si wafer를 기판이자 gate 하부 전극으로 사용하였으며, 열산화 (thermal oxidation)를 통해 두께 100 nm의 SiO2를 절연막으로 형성하였다. 이후 채널 층 증착을 대비하여 불순물을 제거하고 손상을 방지하기 위해 표준 세정 (piranha cleaning)을 진행하였다. Acetone을 이용하여 무기, 유기 불순물을 제거하고 isopropyl alcohol과 탈이온수 (deionized water)를 사용하여 잔류하는 acetone을 세척하였다. 기판상의 먼지처럼 작은 불순물이 아닌 넓은 범위를 차지하는 불순물은 단순히 기포의 파괴에 의해 떨어지기 힘든 경우가 있다. 따라서 초음파 분쇄기(sonicator)를 사용하여 오염 물질과 기판 사이의 틈에 기포를 발생시키고 파괴하거나, 큰 기포를 발생시킴으로써 오염 물질을 기판으로부터 더욱 효과적으로 분리하고 세척하였다.

이후 piranha cleaning을 마친 SiO2 절연막 상에, 산소 결핍 구조의 TiO2-x 채널 층을 증착하기 위해 RF magnetron sputtering system을 이용하여 스퍼터링 증착 공정을 진행하였다. 스퍼터링 시스템은 저/고진공을 형성한 후 진공도를 유지시키기 위한 진공 프로세스 챔버, RF 전원 공급 장치 (RF generator), 스퍼터링 타겟 (target) 소스, 기판 홀더, 가스 주입 장치 (mass flow controller, MFC)로 구성되어 있다. 스퍼터링에 사용된 소스는 단일 TiO2-x로 제조된 직경 4 inch target을 사용하였고, TiO2-x target 면을 음극 (cathode)으로, 기판의 면을 양극 (anode)으로 설정하였으며 기판과 target 사이의 거리를 8 cm로 유지하였다. 스퍼터링 시 초기에 고진공 상태로 도달하기 위해 로터리 펌프 (rotary pump)를 이용하여 프로세스 챔버 내의 압력을 약 2.5 × 10-3 torr까지 조절한 후, 터보 펌프 (turbo molecular pump)를 통해 약 6.5 × 10-6 torr까지 고진공도를 설정하여 초기 압력을 설정하였다. 챔버 내로 고순도의 이온화된 아르곤 (Ar) 가스를 MFC를 통해 약 30 sccm으로 주입하고 가스를 가속하여 TiO2-x target에 충돌시킴으로써 원자를 분출하였다. RF power는 200 W를 인가하여 플라즈마를 유지시킨 후 실제 공정 압력을 약 1.5 × 10-2 torr로 설정하였다. 박막을 증착하기 전에 target 표면에 남아있는 불순물을 제거하기 위해 예비 스퍼터링을 5분 동안 진행한 후, TiO2-x를 약 30 nm 두께로 증착하였다. 이때의 기판 온도는 상온으로 유지하였으며 박막의 균일한 증착을 위해서 기판을 7 rpm의 속도로 회전시켰다.

RF magnetron sputtering system을 통해 TiO2-x 채널층을 증착한 후, RTA의 온도 변수가 TiO2-x 박막에 미치는 영향을 조사하기 위해서 MIDAS사의 RTA system을 이용하여 post-annealing을 진행하였다. RTA는 기판의 온도를 상승시키는 부분에서 인덕터 코일 (inductor coil)을 사용하는 것이 아닌 복사 열전달 (radiation heat transfer)을 이용하므로, 외벽 및 주변은 차가운 상태를 유지하게 되고 주위 제어 (ambient control)가 상대적으로 간단하며 열처리 량 (thermal mass)이 적으므로 열처리 시간을 대폭 줄일 수 있다. 특히 기존의 furnace 방식과 비교하여, RTA는 공정 중에 발생할 수 있는 채널 층의 lifetime degradation 유발을 방지함에 있어서 더욱 수월하다. 따라서 RTA 방식을 채택하여, TiO2-x 채널 층을 30 nm로 증착한 5개의 기판 중에서 4개의 기판에 각각 400, 500, 600, 700 °C로 온도차를 설정하고 약 5분 동안 RTA를 실시하였다.

RTA를 진행한 후, DC magnetron sputtering system을 통해 알루미늄 (Al) target과 source/drain 쉐도우 마스크(shadow mask)를 이용하여 진공상에서 스퍼터링을 진행하였다. DC power와 프로세스 챔버 내에 실제 공정 압력을 각각 150W, 1.5 × 10-2 Torr로 설정한 후, 길이 200 μm, 폭 2,000 μm인 Al source/drain을 TiO2-x 채널 층 상부에 약 100 nm 두께로 증착하여 TiO2-x 채널 층 기반 TFT의 제작을 완성하였다.

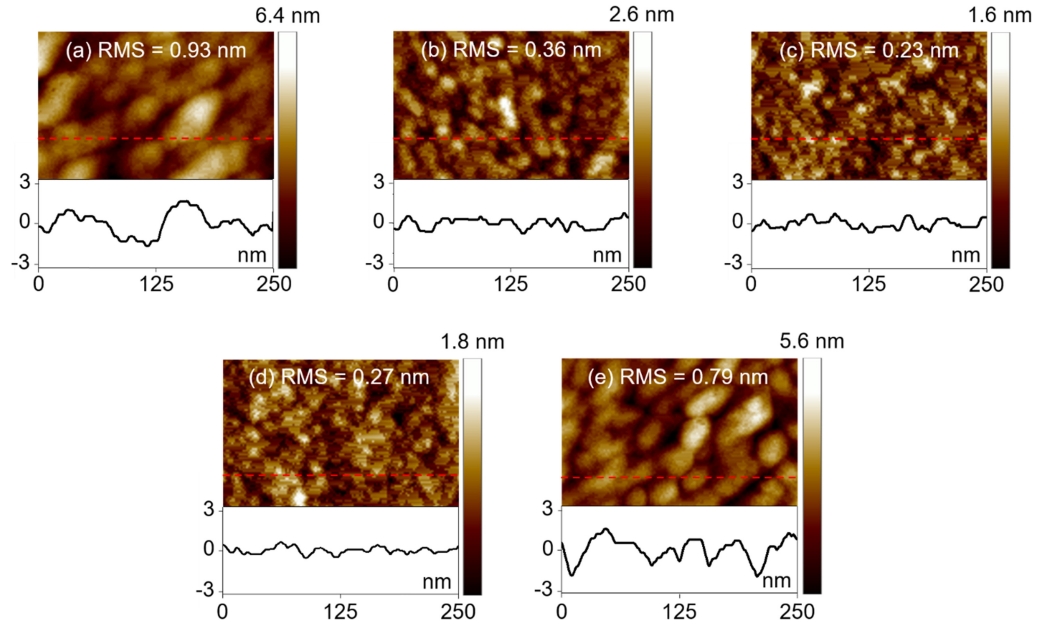

최종적으로 본 연구에서는 RTA를 진행하지 않은 TiO2-x 채널 층 기반의 TFT와 reference post-annealing으로 실시한 RTA 온도차가 400, 500, 600, 700 °C로 각각 다르게 설정된 TiO2-x 채널 층 기반의 TFT를 제작하였다. 완성된 TFT의 비교 분석을 위해서, 실온에서 Keithley사의 반도체 파라미터 분석기 (Keithley 2636)를 통해 각각의 파라미터를 추출하여 트랜지스터로서 전기적 성능과 전류 지속성 및 안정성을 측정하였다. 또한 RTA 온도 변수가 TiO2-x 박막에도 미치는 영향을 조사하기 위해서, BRUKER사의 모델명 ICON AFM (atomic force microscope) 원자간력 현미경을 사용하여 TiO2-x 채널 층의 미세 구조를 분석하였다.

3. 결과 및 고찰

본 연구에서는 TiO2-x 채널 층 기반의 TFT 제작 공정을 진행하는 도중에 post-annealing으로 RTA의 온도차를 임의의 환경 변수로 설정함으로써, 트랜지스터 소자의 특성을 향상시키기 위한 최적화된 조건을 조사하였다.

그림 1(b)은 본 연구에서 제작한 TiO2-x 채널 층에 대한 RTA를 진행하지 않은 as-deposited 소자와 400, 500, 600, 700 °C로 온도차를 각각 설정하여 RTA post-annealing 과정을 거친 TiO2-x 채널 층의 결정성을 확인하기 위해서, Rigaku사의 모델명 JP/SmartLab 고출력 x-선 회절분석기 (x-ray diffractometer, XRD)를 사용한 결과를 나타낸다. 종합적으로 보았을 때, rutile TiO2-x 박막의(110) 면에 해당하는 2 theta = 27.5°에서 강한 peak가 나타나는 것을 관찰할 수 있다. 하지만 XRD 패턴을 보았을 때, 순수한 amorphous 상태의 TiO2-x 박막에 있어서 명확한 peak가 관찰되지 않는 것을 확인할 수 있다. 반면에 진행한 RTA의 온도가 증가함에 따라 점차 XRD peak가 상승하는데, 이와 같은 변화를 통해 박막 증착 후의 RTA가 TiO2-x의 결정을 amorphous에서 rutile 구조로 점차 변화시키는데 중요한 점으로 작용하는 것을 알 수 있다. TiO2-x 박막은 일반적으로 상온 상태에서 제작된 후, 어떠한 crystalline도 띄지 않는 amorphous 형태를 지닌다. 하지만 환경상의 상전이 온도와 압력에 따라서 rutile, anatase, 브루카이트 (brookite)의 세 가지 결정 형태로 변화할 수 있다. Amorphous 형태는 구조적인 불규칙성에 의하여 energy bandgap 내에 상당히 많은 국부 상태(localized state)가 발견되기 때문에 소자의 해석에 어려운 점이 많이 존재한다. 또한 결정 입계 (grain boundary)로부터 발생하는 채널 층의 전하 트랩 (charge trap) 상태로 인해, 부분적으로 전기적 저항 값이 높아서 캐리어의 이동도 및 암전도도가 낮다는 문제점이 있다. 하지만 amorphous에서 rutile 구조로 상변화가 발생하게 되면, 전기적 저항값이 현저하게 줄어들며 대체로 모든 온도에서 안정적인 점으로 인해서 전하 전이 (charge transport)가 매우 높아지므로 최종적으로 트랜지스터의 성능에 전기적으로 우수한 영향을 미친다. 따라서 post-annealing으로 진행한 RTA의 온도가 높아질수록, TiO2-x 채널 층 기반의 TFT에 대한 전자 이동도 (electron mobility)가 개선되는 rutile 구조로 점차 상변화가 진행되는 것을 확인할 수 있다.

그림 2는 as-deposited 소자와 400, 500, 600, 700 °C로 RTA를 실시하여 제작한 TiO2-x 채널 층 기반의 TFT의 전기적 특성을 조사하기 위해서, source-drain bias voltage (Vds)를 0 ~ 30 V까지 step 0.2 V로 설정하였을 때의 source-drain current (Ids)를 조사한 출력 특선 (output curve)을 나타낸다.

위의 식 (1)은 선형 전류 영역 (linear current region)에서의 Ids를 의미하며, Ci는 절연막에서의 단위 면적당 커패시턴스 (capacitance), W와 L은 채널 층의 폭 (width)과 길이 (length), μFE는 전계 효과 이동도 (field effect mobility)를 뜻한다. Ids 값이 매우 낮으면, 식의 이차항을 무시할 수 있고 Vds와 Ids 사이의 선형 관계를 확인할 수 있으므로 이와 같은 상태를 linear current region이라 명칭한다.

식 (2)는 포화 영역 (saturation region)에서의 Ids를 의미하며, μsat는 포화 이동도 (saturation mobility)다. Saturation region에서 n-채널 pinch-off가 발생하고 Ids는 포화 상태에 도달하게 되는데, output curve에서 linear current region과 saturation region을 명확하게 확인할 수 있다. Vgs 값이 상승할수록 Ids-Vds curve 사이의 간격과 μsat도 점차적으로 증가한다.

그림 2의 output curve는 gate bias voltage (Vgs)를 0~30 V까지 sweep 10 V로 설정하였다. 진행한 RTA의 온도가 올라갈수록 누설 전류 (leakage current)가 발생하는 것을 확인할 수 있는데, 전반적으로 발견되는 leakage current는 TiO2-x 박막을 증착할 때 패터닝을 진행하지 않아서 생기는 것으로 사료된다. 또한 output curve를 보았을 때, 5~8 V 이전의 상대적으로 낮은 전압에서 leakage current가 발생하는 양상을 확인할 수 있는데, 이는 Al 상부 전극이 증착되기 전의 상태에서 TiO2-x 채널 층에 대해 RTA를 진행한 부분이 영향을 미쳤을 것으로 판단된다. 따라서 RTA에서 형성된 TiO2-x 박막 내의 활성화된 산소가 상부 전극으로 빠져나가지 못 하게 되며, 이는 환원 상황을 더뎌지게 하고 계면 전위 장벽을 감소시켜 결과적으로 저전압 구동에서 leakage current가 발생하였다고 사료된다.

그림 2(a)와 같이, post-annealing으로 RTA를 진행하지 않은 TiO2-x 채널 층 기반의 TFT는 각각의 Vgs에 따른 output curve의 overlap이 발생함에 따라 전기적 성능이 붕괴되어서 연구 가치가 손실된 것을 알 수 있다. 또한 그림 2(a)와 RTA를 400 °C에서 진행한 TiO2-x 채널 층 기반의 TFT인 2(b)는 높은 저항 상태를 가지는 amorphous 구조 채널 층의 잔류하는 절연 특성으로 인하여, 정상적인 TFT 특성을 나타내지 않았다. 하지만 RTA를 500, 600, 700 °C로 실시한 TiO2-x 채널 층 기반의 TFT인 그림 2(c)~2(e)를 보았을 때, Ids-Vds 특성에서 일반적인 n-type 반도체로 동작하는 것을 확인할 수 있다. 열처리 온도 차로 각각을 비교하였을 때, RTA 온도가 상승할수록 pinch-off가 된 후에 포화 영역 (saturation region)에서 Ids의 전류 점멸비 (on/off current ratio)가 점차 상승하는 것을 볼 수 있다. 특히 그림 2(e)와 같이 700 °C에서 RTA를 진행한 TiO2-x 채널 층 기반의 TFT는 강하게 saturation된 output 특성을 보이며, 본 연구에서 RTA를 진행한 TiO2-x 채널 층 기반의 TFT 중 상대적으로 가장 높은 7.2 × 103 A 값의 on/off current ratio를 확인할 수 있다. RTA 열처리 온도가 증가함에 따라 turn-on voltage 값이 음의 방향으로 이동하면서 동시에 Vds가 증가하는 것을 확인할 수 있다. TiO2-x 박막에 대한 XPS 분석을 통해 O1s peak를 보았을 때, TiO2-x 박막에 가한 RTA 온도가 증가함에 따라서 격자 산소 (lattice oxygen) peak가 증가하는 것을 확인할 수 있다 [28,29]. 반면에 TiO2-x 박막에 가하는 RTA 온도를 상승시킬수록 rutile 형태의 TiO2-x 박막으로 상변이가 진행되며, 산소 공공 (oxygen vacancy)이 증가한다. 이러한 oxygen vacancy는 이중으로 대전된 donor 역할을 수행하기 때문에 전자 농도의 증가와 같은 효과를 가질 수 있다고 사료된다. 결국 전자 농도의 증가와 함께 인가 전압의 증가로 Vds 값이 증가하였다고 판단한다.

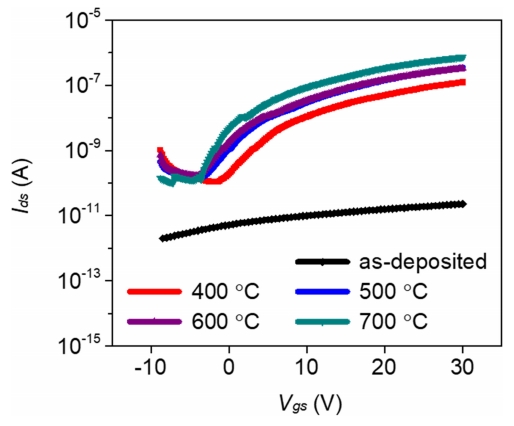

그림 3은 as-deposited 소자와 400, 500, 600, 700 °C로 각각 온도를 설정하고 RTA를 실시하여 제작한 TiO2-x 채널 층 기반의 TFT에 대한 전달 특성 (transfer curve)을 나타낸다. 각각 Vds를 30 V로 고정하여 bias voltage를 인가하였으며, Vgs를 -10~30 V까지 step 0.2 V로 설정하였을 때의 Ids를 조사하였다. RTA를 실시하지 않은 TiO2-x 채널층 기반의 as-deposited TFT는 문턱치 전압 (threshold voltage, Vth)을 계산하는 것이 불가능한 상태로서 transfer 특성이 나타나지 않았다. 또한 on/off 상태의 전류도 매우 낮고, gate 전압에 의한 채널 제어가 어려움으로써 전반적으로 거의 부도체와 같은 특성을 나타냈다. 반면에 RTA를 실시한 TiO2-x 채널 층 기반의 TFT는 Vth가 정상적인 음의 방향으로 크게 변화하며, TFT의 transfer 특성을 나타내는 것을 확인할 수 있다. 이는 RTA를 실시한 과정이 TiO2-x 채널 층과 Al source/drain 사이의 계면 트랩과 TiO2-x 채널 층 내의 결함들을 효과적으로 제거하여 소자의 성능을 향상시킴으로써 발생한 현상으로 사료된다. 또한 RTA를 실시한 TiO2-x 채널 층 기반의 TFT를 각각 비교하였을 때, 실시한 RTA 온도가 상승할수록 off에서 on 상태로 전환되는 속도가 빨라지고 on/off current ratio가 대체로 증가하였으며, 특히 700 °C에서 RTA를 실시한 TiO2-x 채널 층 기반의 TFT의 transfer 특성이 개선되는 것을 확인할 수 있다.

그림 4에서는 본 연구에서 진행한 RTA의 온도 차이가 TiO2-x 채널 층 기반의 TFT에 미치는 영향을 조사하기 위해서 전기적 성능과 신뢰성을 평가하였다.

식 (3)에서 부임계 스윙 (subthreshold swing, S/S)은 Vth 이하의 전압이 인가되었음에도 leakage current가 발생해서 생긴 개념이며, Vgs를 인가하였을 때 출력 값인 Ids를 10배로 생성하는데 필요한 전압의 증가량을 뜻하고 식으로는 Vgs와 logIds의 변화분을 의미한다. S/S 값이 작다는 것은 swing이 적다는 것이며, 역수 값인 slope가 커지고 작은 전압으로도 소자를 off에서 on 상태로 전환할 수 있음을 뜻하기 때문에, S/S 값이 작을수록 우수한 전기적 특성을 가지는 TFT라고 할 수 있다.

식 (4)은 채널이 형성되어 전류가 source에서 drain으로 본격적으로 흐르는 시점의 gate에 bias된 전압인 threshold voltage에 대한 수식이며, Φms는 금속과 반도체의 일함수 차이, Qi와 Ci는 각각 oxide charge, MOSCAP의 capacitor 용량을 뜻한다. Qd·max는 강반전 (onset of strong inversion)일 때의 반도체 내 전하량, φF는 전자 전하량으로 반도체의 중간 레벨인 Ei에서 반도체의 페르미 레벨인 EFs를 뺀 값인 페르미 전위를 뜻하며, 반도체에 얼마나 도핑이 적용되었는지를 나타낸다.

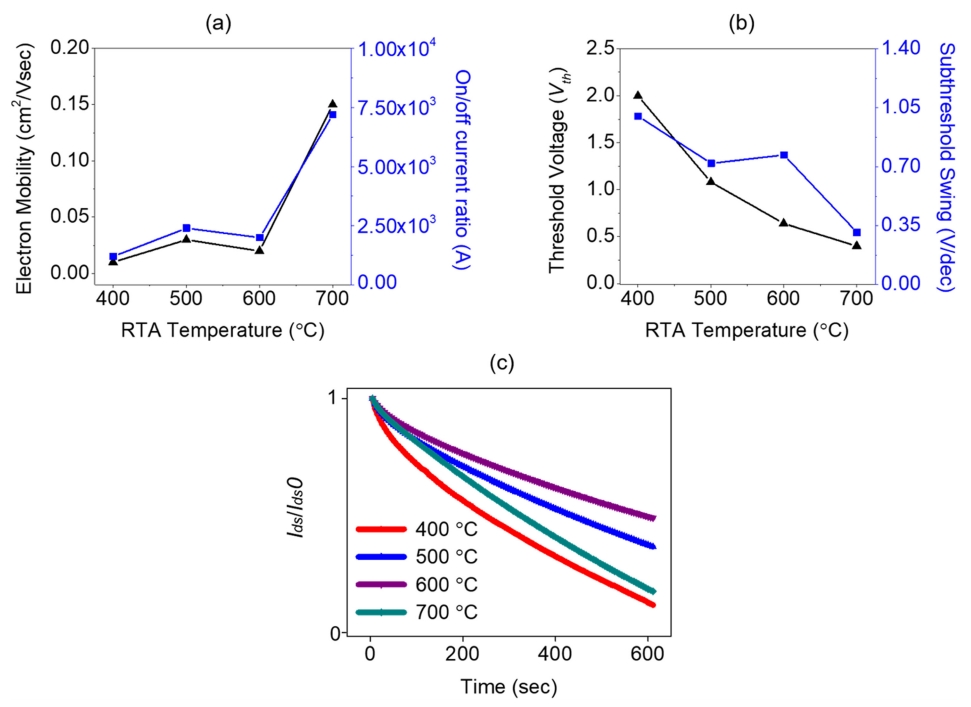

위의 식 (5)은 전자가 얼마나 잘 작동하고 움직이는지를 나타내는 정도인 electron mobility에 대한 수식이며, saturation region에서의 saturation mobility를 의미한다. 그림 4(a) , (b)와 표 1은 400, 500, 600, 700 °C로 RTA를 실시하여 제작한 TiO2-x 채널 층 기반 TFT의 전기적 특성 중 중요시되는 4개의 파라미터에 대해서 그래프와 표로 나타낸 것이다. 4가지 파라미터 기준으로 판단하였을 때, post-annealing으로 RTA를 진행하지 않은 TiO2-x 채널 층 기반의 TFT는 온전한 TFT 성능을 나타내지 않는 것으로 판단된다. RTA 온도가 400 °C에서 점차 상승할수록 TFT 성능이 전반적으로 향상되는 형태를 보이며, 500에서 600 °C로 온도가 올라갈 때 Vth 값이 1.08에서 0.64 V으로 감소하지만 나머지 수치는 비슷한 양상을 보이는 것을 확인할 수 있다. 특히 700 °C에서 RTA를 진행한 TiO2-x 채널 층 기반의 TFT는 Vth가 0.4 V, on/off current ratio로 7.2 × 103A의 값을 가진다. 또한 electron mobility가 0.15 cm2/Vs, S/S로는 0.31 V/dec의 값을 가짐으로써 RTA 온도 400, 500, 600, 700 °C 중에서 가장 우수한 TFT 특성을 보여준다. TiO2-x 채널 층에 대한 열처리가 충분하지 않을 경우에는 박막에 불순물이 다수 잔류하게 되는데, 이와 같은 불순물은 source/drain의 물질로 증착된 Al 전극의 전도성을 떨어뜨리고 녹는점을 낮춤으로써, 온도 상승에 의해 채널 층 쪽으로 쉽게 확산이 되는 원인이 된다. 따라서 400, 500, 600 °C보다 700 °C에서 RTA를 진행한 경우에, 열처리가 보다 충분히 이루어지고 채널 층의 불순물이 더욱 제거되어 온도 의존적인 transfer curve를 나타내는 것을 확인할 수 있다. 그림 4(c)는 400, 500, 600, 700 °C로 RTA를 실시하여 제작한 TiO2-x 채널 층 기반의 TFT에 대해서 Vgs, Vds를 각각 30 V를 지속적으로 인가하였을 때, Ids를 초기 전류 값인 Ids0으로 나눈 값을 통한 TFT의 전기적 신뢰성 (electrical retention stability)을 나타낸다. RTA의 온도가 400, 500, 600 °C로 증가함에 따라 TFT의 단기간 전류 유지 안정성이 비례하여 향상되는 것을 확인할 수 있다. 특히 600 °C에서 RTA를 실시한 TiO2-x 채널 층 기반의 TFT의 전기적 성능은 상대적으로 가장 안정적이며 Ids의 변화량이 적었다. 반면 RTA의 온도가 700 °C로 실시되었을 때, 측정의 마지막인 600 초에서는 Ids가 초기 값에 비해 16.6%까지 하락하였다. 이를 통해 TiO2-x 채널 층이 증착된 후 RTA를 실시하면, anatase에서 rutile 구조로 상변화가 발생하여 rutile 구조의 높은 유전율과 전도도 (conductivity)로 인한 전기적 성능이 향상되는 장점이 있지만, RTA의 온도가 700 °C로 증가함에 따라 오히려 TFT의 안정성 및 신뢰성이 저하되는 것을 확인할 수 있다. 이는 Al source/drain이 증착 될 때 TiO2-x 채널 층에 가해졌던 RTA 온도가 높아질수록 Al sputtering 입자가 기판에 도달할 수 있는 충분한 에너지를 얻을 수 있어서 결정화가 양호하지만, target에서 떨어져 나온 휘발 성분이 쉽게 손실됨에 따라 source/drain이 불완전하게 증착 되어 발생한 단점으로 사료된다.

그림 5는 RTA의 온도 차이가 TiO2-x 채널 층에 미치는 영향을 조사하기 위해서, AFM을 통해 as-deposited 소자와 400, 500, 600, 700 °C로 RTA를 실시하여 제작한 TiO2-x 채널 층의 표면 상태를 250 nm × 250 nm 크기로 측정한 결과이다. RTA를 적용한 후 grain의 크기가 눈에 띄게 작아지는 것을 볼 수 있으며, RTA의 온도가 높아질수록 전반적으로 grain의 크기는 점차 커지고 결정립계 (grain boundary)가 비교적 명확해지는 것을 확인할 수 있다. 그림 5(a)와 같이 RTA를 거치지 않은 TiO2-x 채널 층은 표면 거칠기 (root mean square, RMS)가 0.93 nm로 상대적으로 크게 측정되었다. As-deposited 소자와 비교하였을 때, TiO2-x 채널 층에 RTA를 실시한 경우 RMS가 감소하는 것을 확인할 수 있으며, 특히 실시한 RTA의 온도가 500, 600 °C인 경우에는 RMS가 각각 0.23, 0.27 nm로 상대적으로 표면의 균일도가 우수하다. 반면 그림 5(e)와 같이 RTA를 700 °C로 실시한 TiO2-x 채널 층의 경우에는 오히려 RMS가 증가하는 것을 확인할 수 있다. 채널 층 표면 상의 거칠기가 클수록 전자의 이동을 방해하는 계면 트랩 전하 (interface trap charge) 현상이 일어나고 leakage current 발생에 더욱 일조하여, 소자의 전하 이동도를 감소시키는 원인이 된다 [30]. 따라서 RTA의 온도가 높아질수록 grain의 크기가 증가하고 선명한 grain boundary 확인이 가능함으로써, charge trapping sites를 제거하여 TiO2-x 채널 층 기반 TFT의 고질적인 전기적 특성 저하를 개선할 수 있지만, 700 °C 이상의 RTA 온도에서는 표면상의 거칠기가 증가하여 leakage current 발생을 의도하였다.

4. 결 론

본 연구에서는 RF magnetron sputtering을 이용하여 TiO2-x 채널 층을 증착한 후, RTA의 온도 차이가 TiO2-x 채널 층 기반의 TFT에 미치는 영향을 조사하기 위해 각각 400, 500, 600, 700 °C로 온도 변수를 설정하여 RTA를 진행하였다. XRD 패턴을 보았을 때, post-annealing으로 적용된 RTA의 온도가 증가함에 따라 27.5°에서 XRD peak가 점차 상승하며 TiO2-x의 결정 상태가 amorphous에서 rutile 구조로 상변화 되는 것을 확인하였다. 또한 output, transfer curve를 보았을 때, RTA 온도가 높아질수록 TiO2-x 상 변화의 영향으로 높은 유전율과 conductivity로 인한 TiO2-x 채널 층 기반 TFT의 전기적 성능이 전반적으로 향상되었으며, 특히 RTA 700 °C인 경우 가장 우수한 전기적 성능을 보였다. AFM 측정 결과로 RTA의 온도가 높아질수록 grain 크기가 증가하고, grain boundary가 비교적 뚜렷해지며 표면 상의 거칠기도 감소하였다. 하지만 RTA의 온도가 700 °C로 증가하게 되면, TFT의 안정성 및 신뢰성이 저하되고 표면 상의 거칠기가 커져서 leakage current 발생과 함께 소자의 전하 이동도가 저하되는 것을 확인하였다.