레이저 후열처리 공정을 통한 저온공정형 IGZO 박막 트랜지스터의 특성 개선에 관한 연구

Abstract

High-performance thin-film transistors (TFTs) produced at low temperatures are required for ultrahigh-resolution and flexible display applications. The scientific community has been studying unconventional techniques to investigate low voltage flexible devices and low power flexible circuits for the past decade. In particular, metal oxide semiconductors, such as indium gallium zinc oxide (IGZO), have made significant progress as amorphous silicon replacements for electronics and commercial displays. On the other hand, developing metal oxide transistors with low processing temperatures remains a difficulty. The high-temperature annealing process causes very instability in the plastic substrate. Here, we introduce IGZO TFTs that shows enhanced electrical properties environmental stability by laser post-annealing. After annealing process, the laser post-annealing process was given at 80 MHz, pulse width 140 fs, for 50 seconds. The improved electrical characteristics of this laser post-annealed IGZO TFTs were: 9.03 cm2/Vs; 2.2×107 on/off current ratio. The IGZO TFT to which laser post-annealing was applied had a flat surface, and it was confirmed that the combination of internal metal and oxygen was urged, and the leakage current problem was improved by suppressing excessive generation of oxygen vacancy. Furthermore, the voltage transfer curve was measured after fabricating the N-MOS logic inverter circuit, this inverter showed a value of 80.8% the total noise margin.

Key words: metal oxide transistor, IGZO, laser annealing, post-annealing, logic inverter

1. 서 론

최근 전자·정보 산업의 발달에 따라 IGZO (indiumgallium-zinc-oxide) 금속 산화물 반도체가 플렉시블 및 투명 디스플레이 적용 소재로 크게 주목받고 있다 [ 1- 5]. IGZO 활성층 기반 TFT (thin-film transistor)의 경우, 제조 공정의 온도가 비교적 낮으며, 가시광을 투과하여 투명한 디바이스로의 응용이 가능하기 때문이다. 플렉시블 디스플레이는 플라스틱 기판 기반의 가볍고 깨지지 않으며 형태의 변형이 가능한 소재가 주로 사용되고 있으며 [ 4- 7], sputtering과 solution 공정을 기반으로 한 IGZO 박막 증착 및 열처리 공정 기법에 대한 결과가 많이 발표되고 있다. 하지만 150~200°C 이상의 고온 공정은 플라스틱 기판에 굉장히 불안정한 환경을 제공하며 [ 6- 9], 열처리 과정 중 다양한 화학적 변형이 일어나 디바이스의 안정성을 저하시킬 수 있다 [ 8- 10]. 이러한 화학적 변형이나 디바이스의 안정성 저하 문제를 해결하기 위해 저온 열처리 공정법 혹은 짧은 시간 안에 수행되는 열처리 공정법이 많이 연구되고 있다 [ 11- 17]. 특히, 레이저를 이용한 열처리 공정은 국부적인 스팟 형태의 범위에 레이저가 조사되기 때문에 열 충격을 완화할 수 있으며, 미세공정에 유리하고 레이저와 표면의 상호반응에 따라 산화물 소재의 구조 변화를 방지할 수 있다 [ 18- 20]. 또한, 짧은 파장을 가지는 레이저 조사는 광자의 에너지가 높아 고분자 물질을 열 충격 없이 분해할 수 있고, 레이저 펄스폭이 조사받는 부위의 열 전달 시간보다 짧게 되면 열적 손상 및 구조변화에 영향을 미치지 않는 장점이 있다 [ 20- 22]. 본 논문에서는 매우 짧은 파장의 펨토초 레이저 시스템을 이용하여 낮은 온도에서의 열처리 공정을 마친 소자에 대해 추가적인 레이저 빔 기반의 후처리 공정을 실시하여 IGZO TFT를 제작하였으며, 높은 온도에서의 열처리 공정을 대신하여 플렉시블 및 투명 디스플레이 기판에의 적용성을 평가하였다.

2. 실험 방법

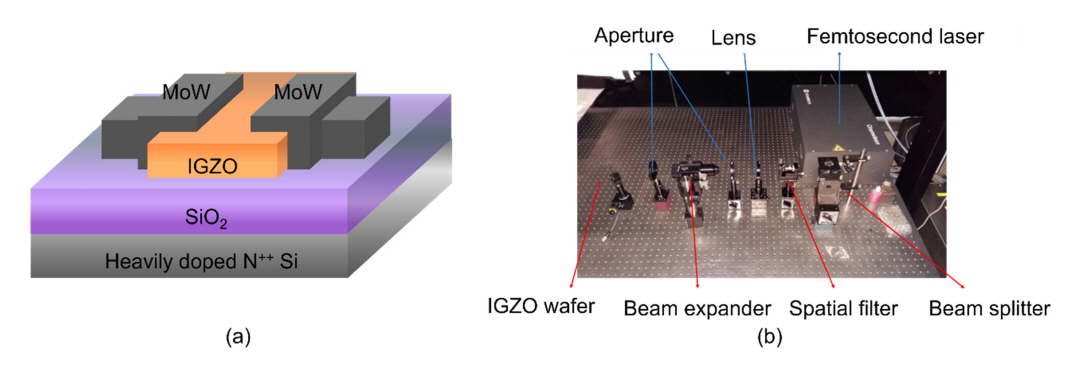

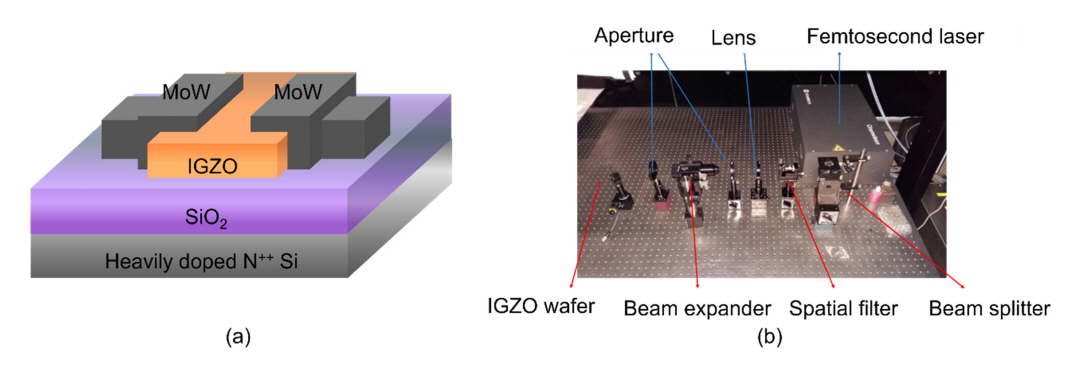

그림 1(a)는 본 연구에서 제작한 IGZO 활성층 기반 TFT의 구조를 나타낸다. heavily doped n-type Si wafer 기판을 gate 전극으로 사용하며, 100 nm SiO 2 층을 TFT의 절연층으로 사용하였다. 그 후, 표면에 남아 있는 불순물들을 제거하기 위한 piranha cleaning과 acetone과 isopropyl alcohol에 담가 20분간 sonication cleaning을 실시하였다. Cleaning을 마친 wafer에 활성층인 IGZO 박막을 sputtering 공정을 이용해 증착하였으며, In:Ga:Zn가 1:1:1 mol.%로 조성된 4인치 source를 사용하였다. Sputtering 공정 이전 불순물 제거 및 Ar 플라즈마를 발생시키기 위해 챔버 내부 진공도를 3.0×10 -6 torr 이하로 조성하였다. Sputtering 공정을 위해 30 sccm의 Ar gas 를 주입한 상태에서 RF power를 150 W 인가하여 4분간 50 nm의 IGZO 박막을 증착하였다. 이 과정에서 wafer와 sputtering source간의 거리는 7 cm 및 기판 회전 속도는 7 RPM으로 고정하였다. 증착을 마친 wafer를 box furnace에서 180°C로 1시간동안 열처리 공정을 실시하였다.

그림 1(b)는 본 연구에서 사용한 레이저 공정 시스템을 보여준다. IGZO 박막이 받는 열 데미지와 구조 변화를 최소화하기 위해 Ti:Sapphire laser system (Coherent, Chameleon Ultra-II)을 사용하여 평균 출력은 3 W, 80 MHz, 펄스 폭은 140 fs으로 고정하여 50초간 조사하였다. 레이저는 공간 필터와 렌즈를 통해 빔의 퍼짐없이 소자에 조사되었으며, 조사된 빔이 빔 익스팬더를 통과하고 레이저가 기판에 완전히 조사되기 위해서 빔을 적절한 크기로 확산시켰다. 레이저를 통해 후열처리 공정을 실시한 이후, DC magnetron sputtering 공정으로 IGZO 활성 층 상부에 100 nm 두께의 MoW source/drain 전극을 증착하여 길이 (L) 200 μm, 폭 (W) 2,000 μm size의 채널 층을 형성하였다.

최종적으로 본 연구에서는 낮은 온도에서의 열처리 공정 이후 어떠한 후열처리공정을 진행하지 않은 IGZO 활성층 기반 TFT 소자와 레이저 후열처리 공정을 수행한 TFT 소자를 비교·분석하였다. TFT의 전기적 성능 변화 비교 분석을 위해, 암실에서 반도체 파라미터 분석기 (Keithley, Keithley 4200)를 통해서 각각의 파라미터를 추출하여 전기적 성능을 측정하였으며, IGZO inverter의 반전 성능을 확인하였다. 또한 IGZO 박막의 표면적 변화를 조사하기 위해, AFM Image를 측정하여 IGZO 박막의 표면 거칠기를 분석하였다. 마지막으로 레이저 후열처리 공정 따른 IGZO 박막 내의 O1s peak 변화를 XPS분석을 통해 측정하였다.

3. 결과 및 고찰

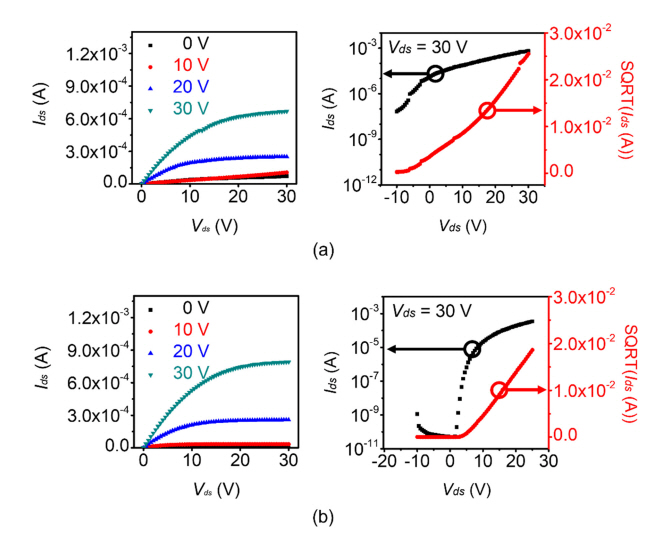

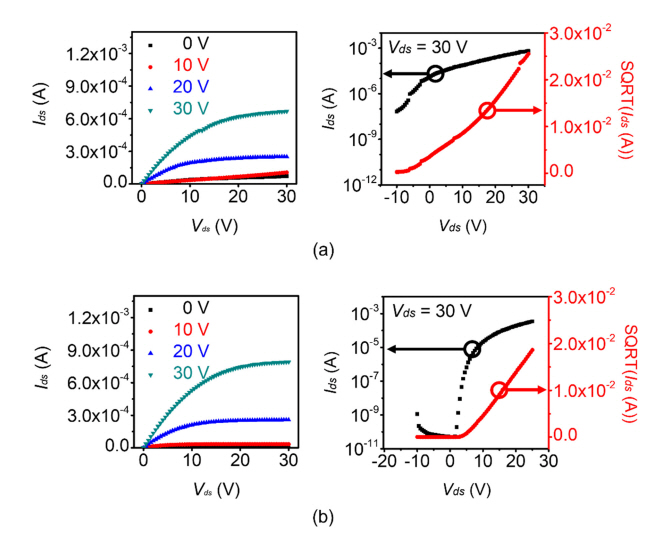

그림 2는 레이저 후열처리 공정을 진행하지 않은 (w/o) IGZO 활성층 기반 TFT와 레이저 후열처리 공정을 진행한 (with) IGZO 활성층 기반 TFT의 전기적 성능을 평가하기 위해 측정한 output & transfer characteristic curve이다. Output characteristic curve는 source-drain bias voltage ( Vds)를 0~30 V까지 sweep 10 V, step 0.5 V로 설정하였을 때의 source-drain current ( Ids)을 측정한 결과이며, transfer characteristic curve는 Vds를 30 V 인가한 상태에서 source-gate voltage ( Vgs)를 0~30 V 0.5 step voltage를 인가하였을 때의 Ids를 측정하였다. TFT의 전기적 성능 분석을 위한 중요 파라미터 4가지는 아래 식으로부터 유도하였다.

liner region에서의 Ids

saturation region에서의 Ids

180°C의 열처리 공정 후 레이저 후열처리 공정을 진행하지 않은 소자의 경우, 포화 상태 영역에서 굉장히 불안정함을 확인할 수 있다. 열처리 과정이 hot-walled 방식으로 진행되었기 때문에, furnace 내부에 오염 물질이 조금이라도 잔존한다면 열처리 과정에서 IGZO 박막에 전이될 수 있는 가능성이 존재하며, 낮은 열처리 온도로 인해 IGZO 박막이 평탄화가 진행되지 못하였고, 다수의 defect과 trap site를 가지고 있을 것이라 판단되며, 이에 따라 포화 상태 영역에서의 불안정성을 야기시켰다고 할 수 있다 [ 23, 24]. 이와 같은 포화 상태 영역의 불안정성은 많은 양의 누설 전류를 야기시킨 것을 볼 수 있다. 그에 비해, 레이저 후 열처리를 진행한 소자의 경우, 포화 상태 영역에서 대체로 안정적이었으며, 레이저 후열처리로 인해 표면의 defect과 trap site를 효과적으로 제거한 영향으로 사료된다 [ 25, 26].

표 1은 TFT의 전기적 특성 중 분석에 중요 4개의 파라미터에 대해 정리한 것이다. 레이저 후열처리 공정을 진행하지 않은 소자의 경우, 낮은 온도에서의 열처리 공정으로 인해 IGZO 박막이 완전한 결정화가 이루어지지 않아 매우 불안정한 상태를 보였으며, 전류 점멸비 ( Ion/ Ioff)가 9.4×10 3의 값을 보였으며, 문턱전압 ( Vth)와 문턱전압 이하에서의 기울기 ( S/S) 또한 transistor 소자로 사용되기에 부적합한 성능을 보였다. 그러나, 레이저를 사용하여 후열처리 공정을 진행한 소자는 Ion/ Ioff가 2.2×10 7으로 개선되었으며, Vth와 S/S 또한 준수한 값을 보였다. 이는 낮은 온도에서의 열처리 공정으로 인해 표면 경화와 열 완화가 제대로 이루어지지 못한 소자는 활성층과 절연층 계면에 불특정한 준위로 electron tunneling 현상이 발생하게 되고, flatband voltage의 shift가 발생하기 때문이다 [ 27- 29]. 전기적 성능 분석을 통해 레이저 후열처리 공정이 IGZO 박막의 불안정성을 완화시키고, electron tunneling 현상 억제에 효과가 있음을 확인하였으며, 레이저 후열처리 공정이 IGZO 활성층 박막에 미치는 영향을 더욱 자세하게 분석하기 위해, IGZO 성분, 표면 분석 평가를 수행하였다.

레이저 후열처리 공정을 진행하지 않은 IGZO 활성층 박막과 레이저 후열처리 공정을 진행한 IGZO 박막의 표면적 성능을 분석하기 위해 측정한 AFM image를 그림 3에 나타내었다. 후열처리 공정을 진행하지 않은 그림 3(a)의 IGZO 활성층 박막의 경우, 표면 단차가 비교적 크며, 표면의 크고 작은 불규칙한 particle들 또한 확인할 수 있다. 이는 IGZO 박막이 낮은 온도에서 완전히 경화되지 못하고, 부분적으로 경화되어 평탄화 되지 못한 것으로 보인다. 그림 3(b)를 통해 레이저 후열처리 공정 이후 부분적으로 경화되어 평탄하지 못했던 표면에 존재하던 미세 입자와 불순물이 효과적으로 제거되어 균일도가 높아지고 전반적으로 매끄러워졌으며, 평탄해진 것을 확인할 수 있다. RMS 값 또한 개선되었는데, 활성층 표면이 거칠수록 interface charge trap 현상이 일어나고 leakage current가 발생하여, 디바이스의 전기적 성능과 안정성을 저하시키는 주된 원인이 된다 [ 30- 32]. AFM image 분석을 통해, 낮은 온도에서의 열처리 공정 이후 레이저 후열처리 공정을 실시하는 경우, IGZO 박막 거칠기를 감소시켜 계면 특성을 향상시키고 interface charge trap 현상을 억제하여 IGZO TFT의 전기적 특성을 개선할 수 있다 [ 30, 33].

그림 3(c)는 레이저 후열처리 공정 전후에 따른 IGZO 박막의 결정화를 알아보기 위해 측정한 XRD data 결과이다. 국부 영역에 집중되는 레이저를 통한 고에너지가 박막의 결정화를 유도할 수 있다 [ 11, 34- 37]. XRD data 분석 결과, 레이저 후열처리를 수행한 IGZO 박막의 경우 (009) peak (2θ=30.84o), (0012) peak (2θ=41.52o)에서 peak가 검출되었다. 이를 통해 레이저 후열처리가 IGZO 박막의 결정화를 유도했음을 확인하였으며, [ 35- 37] IGZO 박막의 결정화를 통해 TFT의 성능이 개선되었음을 확인하였다.

레이저 후열처리 공정 여부에 따른 IGZO 박막의 O1s peak 변화를 분석하기 위해 XPS를 측정하였으며, 그 결과는 그림 4에 나타내었다. 레이저 후열처리 공정 이후 전체 O1s 피크에서 격자 산소 (lattice oxygen) 피크 ( O1)의 비중이 약 46.2%에서 55.7%로 증가하였으며, 전체 O1s 피크에서 산소 공공 (oxygen vacancy) 피크 ( O2)와 하이드록사이드 (hydroxide) 피크 ( O3)는 각각 비중은 약 36.4%에서 30.8%로, 17,4%에서 13.5%로 감소하였다.

O2 피크가 커지는 경우, 금속과 산소 간의 결합이 충분하게 이루어지지 않은 채로 oxygen vacancy가 잔류되어 전자 농도가 커짐에 따라서 전도도가 증가하며 leakage current의 증가로 인해 TFT의 성능이 하락하게 된다 [ 38, 39]. O3 피크가 커지는 경우, 산소 공공에 수소 이온들이 결합해서 수소와 상대적으로 강하게 결합되어있는 trap site가 증가하고 interface charge trap 현상이 더욱 많이 발생하게 된다 [ 31, 32, 40, 41]. 또한 이는 leakage current 발생에 일조하며 소자의 전하 이동도를 감소시키는 원인이 되기 때문에, 결과적으로 TFT의 전기적 성능이 전반적으로 하락하게 된다. 결과적으로 레이저 후열처리 공정은 불안정하고 결합이 부분적으로 수행된 IGZO 박막의 내부 금속과 산소의 결합을 촉구하고, oxygen vacancy의 과도한 생성을 억제하여 그로 인해 leakage current 문제를 개선시키는 것을 알 수 있다

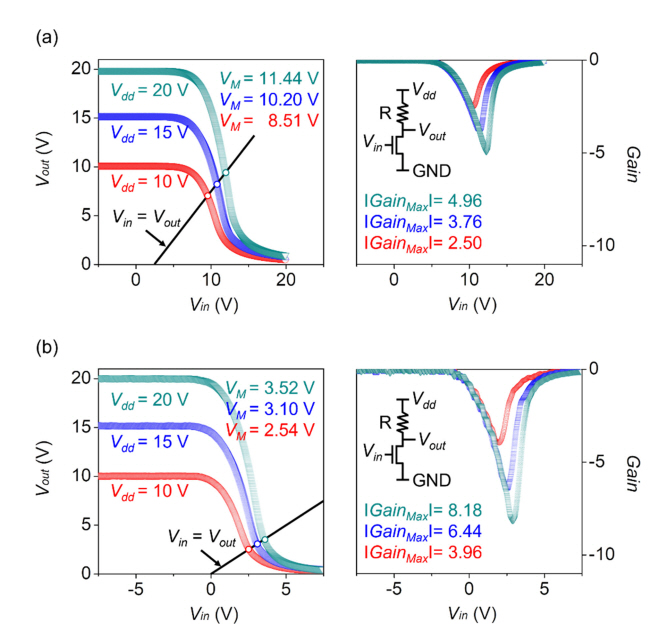

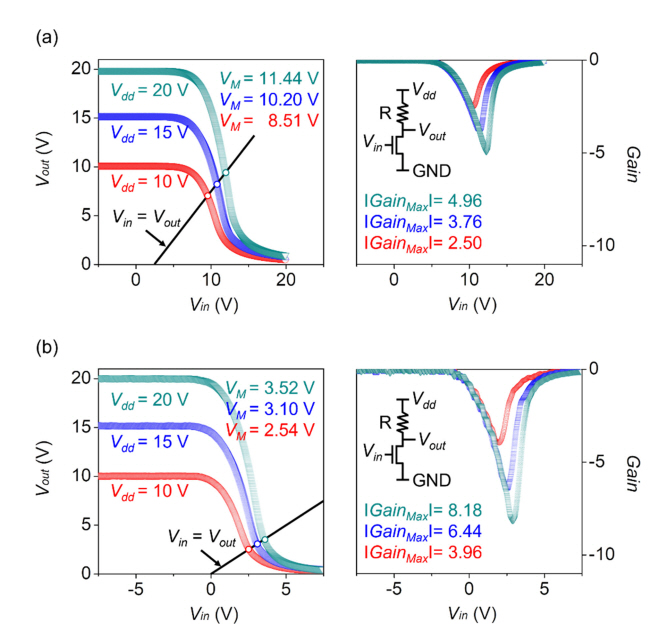

그림 5는 본 연구에서 제작한 IGZO 활성층 기반 TFT와 1 MΩ의 부하 저항을 사용하여 N-MOS logic inverter circuit을 제작한 후 측정한 voltage transfer curve와 static gain 값을 보여준다. 그림 5(a)와 그림(b)는 레이저 후열처리 공정 유무에 따른 static test 측정 결과이다. 좌측 그림을 통해 output high voltage ( VOH) 값은 Vdd 값에 일치하며, output low voltage ( VOL) 값은 0 V에 도달한 curve를 확인할 수 있으며, 우측 그림은 Δ Vout/Δ Vin으로 계산된 gain curve 이며, gain curve에서의 피크는 inverter의 transition point를 나타내고 있다. 그림 5(a)의 레이저 후열처리를 수행하지 않은 디바이스의 경우, Vdd = 10 V 일 때 VM = 8.51 V에서 2.5의 Gain max 값을 보였으며, 비교적 높은 전압이 인가되어야 inverting이 일어났다.

반면, 그림 5(b)의 레이저 후열처리를 적용한 소자의 경우, Vdd=10 V, 20 V가 인가되었을 때, Gain max 값은 각각 VM=2.54 V에서 3.96, VM=3.52 V에서 8.18의 결과를 보였다. 또한, Inverter의 noise margin [ 42- 44] 특성을 분석하기 위해, 20 V의 Vdd를 인가하였을 때의 curve로부터 input high voltage ( VIH)와 input low voltage ( VIL)를 추출하였으며, 표 2에 나타내었다. 레이저 후열처리 공정을 적용한 디바이스의 경우, 추출된 VIH와 VIL의 값은 각각 4.58 V, 0.44 V이며, high margin ( NMH= VOH− VIH)과 low margin ( NML= VIL− VOL)을 대입하여 total noise margin (( NMH+ NML)/ Vdd) [ 42- 44] 값을 추출한 결과는 80.8%로 레이저 후열처리 공정을 적용하지 않은 디바이스에 비해 약 20% 향상된 성능을 보였다.

4. 결 론

본 논문에서는 낮은 온도의 열처리 공정 이후 레이저 시스템을 이용하여 추가적으로 후열처리 공정을 수행하여 IGZO TFT에 어떠한 영향을 미치는지 분석하였다. 낮은 온도에서의 열처리 공정으로 인해 불안정한 전기적 성능을 보인 IGZO TFT가 레이저 후열처리 공정으로 인해 안정되었으며, defect과 trapping 문제가 개선되었다. IGZO 박막의 표면 상태를 주사전자현미경으로 분석했을 때, 레이저 후열처리를 진행하지 않은 IGZO 활성층과 비교하여 후열처리를 진행한 IGZO 활성층은 표면에 존재하던 불순물이 효과적으로 제거되어 표면 균일도가 높고 평탄하였다. 또한, 레이저 후열처리 공정 이후 불안정하고 결합이 부분적으로 수행된 IGZO 박막 내부 금속과 산소의 결합이 촉진되었으며, oxygen vacancy를 제어하여 leakage current 문제를 개선시키는 결과를 확인하였다. N-MOS logic inverter circuit을 이용한 voltage transfer characteristic curve 측정을 통해 소자의 반전 특성을 확인하였으며, total noise margin 값을 추출하였을 때, 레이저 후열처리 공정 적용 후 약 20 % 향상된 결과를 보여 논리 회로에 실제 적용 가능성이 있다고 판단하였다.

Acknowledgments

This research was supported by the MSIT (Ministry of Science and ICT), Korea, under the Grand Information Technology Research Center support program (IITP-2021-2020-0-01462) supervised by the IITP (Institute for Information & communications Technology Planning & Evaluation), by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (No. 2020R1A6A1A12047945), and by the Chungbuk National University BK21 program (2021).

Fig. 1.

(a) Schematic diagram of IGZO active layer-based TFT, and (b) laser system (Ti:Sapphire laser system (Coherent, Chameleon Ultra-II)).

Fig. 2.

Output & transfer characteristics Ids – Vgs curves of IGZO TFTs by laser post-annealing (a) without post-annealing, and (b) with post-annealing.

Fig. 3.

AFM images of the IGZO TFTs by laser post-annealing (a) without post-annealing, and (b) with post-annealing, and (c) XRD diffraction patter of IGZO films with and without post-annealing.

Fig. 4.

XPS spectra O1s peaks of the IGZO TFTs by laser post-annealing with or without laser post-annealing process (a) without post-annealing, (b) with post-annealing, and (c) distribution of O1s Peak by area.

Fig. 5.

Voltage transfer characteristic curves of IGZO TFTs, and signal gain of the N-MOS inverter for supply voltages (a) without post-annealing, and (b) with post-annealing.

Table 1.

Electrical properties of IGZO TFTs by laser post-annealing with and without post-annealing.

|

Laser post-annealing |

µsat (cm2/Vs) |

Ion/Ioff

|

Vth (V) |

S/S (V/dec) |

|

w/o |

9.26 |

9.4 ⅹ 103

|

9.34 |

2.24 |

|

w/ |

9.03 |

2.2 ⅹ 107

|

6.70 |

0.89 |

Table 2.

Voltage specifications of IGZO TFTs by laser post-annealing with and without post-annealing.

|

Laser post-annealing |

VIH (V) |

VIL (V) |

VOH (V) |

VOL (V) |

Total noise margin (%) |

|

w/o |

13.98 |

8.31 |

20.00 |

0.90 |

67.10 |

|

w/ |

3.95 |

0.61 |

20.00 |

0.50 |

80.80 |

REFERENCES

1. D. H. Lee, K. Nomura, T. Kamiya, and H. Hosono, IEEE Electron Device Lett. 32, 1695 (2011).  2. M. M. Billah, M. M. Hasan, and J. Jang, IEEE Electron Device Lett. 38, 890 (2017).  3. J.-S. Park, T.-W. Kim, D. Stryakhilev, J.-S. Lee, S.-G. An, Y.-S. Pyo, D.-B. Lee, Y. G. Mo, D.-U. Jin, and H. K. Chung, Appl. Phys. Lett. 95, 013503 (2009).  4. C. W. Chien, C. H. Wu, Y. T. Tsai, Y. C. Kung, C. Y. Lin, P. C. Hsu, H. H. Hsieh, C. C. Wu, Y. H. Yeh, C. M. Leu, and T. M. Lee, IEEE Trans. Electron Devices. 58, 1440 (2011).  5. W. B. Jackson, R. L. Hoffman, and G. S. Herman, Appl. Phys. Lett. 87, 193503 (2005).  6. S. Ho, H. Yu, and F. So, Appl. Phys. Lett. 111, 212103 (2017).  7. J. Kaczmarski, A. Taube, M. A. Borysiewicz, M. Myśliwiec, K. Piskorski, K. Stiller, and E. Kamińska, IEEE Trans. Electron Devices. 65, 129 (2018).  8. T. Kamiya, K. Nomura, and H. Hosono, Sci. Technol. Adv. Mater. 11, 044305 (2010).  9. K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature. 432, 488 (2004).   10. Y.-J. Lin, H.-Y. Lee, F.-T. Hwang, and C.-T. Lee, J. Electron. Mater. 30, 532 (2001).   11. Y. Yang, S. S. Yang, and K. Chou, IEEE Electron Device Lett. 31, 969 (2010).  12. B. D. Ahn, W. H. Jeong, H. S. Shin, D. L. Kim, H. J. Kim, J. K. Jeong, S.-H. Choi, and M.-K. Han, Electrochemical and Solid-State Letters. 12, H430 (2009).  13. M. Nakata, K. Takechi, T. Eguchi, E. Tokumitsu, H. Yamaguchi, and S. Kaneko, Jpn. J. Appl. Phys. 48, 081607 (2009).  14. M. Nakata, K. Takechi, K. Azuma, E. Tokumitsu, H. Yamaguchi, and S. Kaneko, Appl. Phys. Express. 2, 021102 (2009).  15. Y. H. Yang, S. S. Yang, and K. S. Chou, J. Soc. Inf. Disp. 19, 247 (2011).  16. Y.-S. Kim, J.-Y. Choi, S.-H. Choe, B.-C. Cha, Y.-M. Kong, and D. Kim, Korean J. Met. Mater. 58, 190 (2020).   17. D. Park, Y. Yang, and K. Kim, Korean J. Met. Mater. 59, 209 (2021).   18. T. Sameshima, S. Usui, and M. Sekiya, IEEE Electron Device Lett. 7, 276 (1986).  19. K. Sera, F. Okumura, H. Uchida, S. Itoh, S. Kaneko, and K. Hotta, IEEE Trans. Electron Devices. 36, 2868 (1989).  20. M. Kasischke, E. Subaşı, C. Bock, D.-V. Pham, E. L. Gurevich, U. Kunze, and A. Ostendorf, Appl. Surf. Sci. 478, 299 (2019).  21. A. V. Pavlikov, P. A. Forsh, S. E. Svyakhovskiy, A. N. Matsukatova, E. A. Forsh, A. G. Kazanskii, and P. K. Kashkarov, Appl. Phys. Lett. 113, 203103 (2018).  22. W. Perrie, A. Rushton, M. Gill, P. Fox, and W. O’Neill, Appl. Surf. Sci. 248, 213 (2005).  23. X. Zeng, J. Zhang, and F. Huang, J. Appl. Phys. 111, 123525 (2012).  24. W. Liu, W. Li, Z. Hu, Z. Tang, and X. Tang, J. Appl. Phys. 110, 013901 (2011).  25. W. Choi, H. Y. Kim, J. W. Jeon, W. S. Chang, and S.-H. Cho, Materials. 10, 212 (2017).  26. L. Hong, X. C. Wang, H. Y. Zheng, H. Wang, and H. Y. Yu, Appl. Surf. Sci. 297, 134 (2014).  27. S. G. Jung, K. W. Lee, K. S. Kim, S. W. Shin, S. S. Lee, J. C. Om, G. H. Bae, and J. H. Lee, IEEE Trans. Electron Devices. 55, 1020 (2008).  28. B. Zhang, S. Xie, J. Xu, Q. Qian, Z. Zhang, and K. Xu, IEEE Trans. Ind. Electron. 64, 9052 (2017).  29. K. Endo, S. I. O. uchi, Y. Ishikawa, Y. Liu, T. Matsukawa, K. Sakamoto, M. Masahara, J. Tsukada, K. Ishii, H. Yamauchi, and E. Suzuki, IEEE Electron Device Lett. 30, 757 (2009).  30. Y. Jiang, T. Narushima, and H. Okamoto, Nat. Phys. 6, 1005 (2010).   31. T. Hosoi, K. Kutsuki, G. Okamoto, M. Saito, T. Shimura, and H. Watanabe, Appl. Phys. Lett. 94, 202112 (2009).  32. K. Iwamoto, Y. Kamimuta, A. Ogawa, Y. Watanabe, S. Migita, W. Mizubayashi, Y. Morita, M. Takahashi, H. Ota, T. Nabatame, and A. Toriumi, Appl. Phys. Lett. 92, 132907 (2008).  33. T. Takada, Y. Hayase, Y. Tanaka, and T. Okamoto, IEEE Trans. Dielectr Electr Insul. 15, 152 (2008).  34. C.-Y. Tsay, M.-C. Wang, and S.-C. Chiang, J. Electron. Mater. 38, 1962 (2009).  35. Y. Shin, S. T. Kim, K. Kim, M. Y. Kim, S. Oh, and J. K. Jeong, Sci. Rep. 7, 1 (2017).   36. S.-K. Jeong, M.-H. Kim, S. Lee, H. Seo, and D.-K. Choi, Nanoscale Res. Lett. 9, 619 (2014).   37. T. Chen, M.-Y. Wu, R. Ishihara, K. Nomura, T. Kamiya, H. Hosono, and C. M Beenakker, J. Mater. Sci. Mater. Electron. 22, 1694 (2011).  38. A. Grimaud, O. Diaz-Morales, B. Han, W. T. Hong, Y.-L. Lee, L. Giordano, K. A. Stoerzinger, M. T. M. Koper, and Y. Shao-Horn, Nat. Chem. 9, 457 (2017).   39. S. Patil, S. Seal, Y. Guo, A. Schulte, and J. Norwood, Appl. Phys. Lett. 88, 243110 (2006).  40. Y. Hou, Z. Wen, S. Cui, X. Feng, and J. Chen, Nano Lett. 16, 2268 (2016).  41. R. Ma and T. Sasaki, Adv. Mater. 22, 5082 (2010).  42. K. Wu, S. Zhang, Z. Xu, X. Chen, and L. Li, IEEE Trans. Electron Devices. 62, 4220 (2015).  43. L. Kergoat, L. Herlogsson, B. Piro, M. C. Pham, G. Horowitz, X. Crispin, and M. Berggren, Proc. Natl. Acad. Sci. 109, 8394 (2012).  44. J. B. Kim, C. Fuentes-Hernandez, S. J. Kim, S. Choi, and B. Kippelen, Org. Electron. 11, 1074 (2010).

|

|